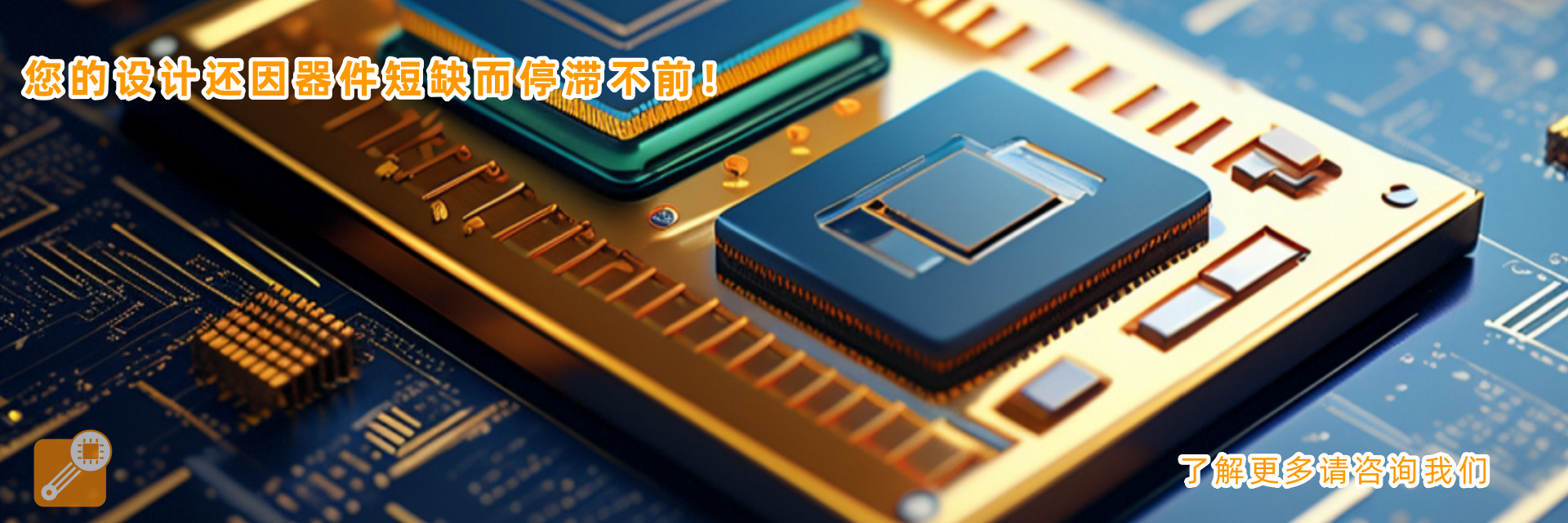

FPGA运算单元现如今 已可以 支持高算力浮点

2024-10-26伴随着深度学习(MachineLearning)行业愈来愈多地应用当场程序控制器门阵列(FPGA)来开展逻辑推理(inference)加快,而传统式FPGA只支持指定运算的短板愈发突显。Achronix以便处理这一大窘境,自主创新地设计方案了深度学习CPU(MLP)单元,不但支持浮点的乘加运算,还能够支持对多种多样定浮点数格式开展分拆。 MLP全名MachineLearningProcessing单元,是由一组最多32个乘法器的列阵,及其一个加法树、累加器、也有四舍五入rounding/饱和状